- L’analyseur de qualité de signal MP1900A d’Anristu a été mis en oeuvre dans le cadre d’un système de test PCI-Express 6.0 Base Specification, avec l’oscilloscope temps réel DPO70000SX de Tektronix et l’IP PCI Express 6.0 de Synopsys.

- Cette démonstration a été effectuée lors de la conférence des développeurs PCI-SIG au centre de convention de Santa Clara, les 21 et 22 juin 2022.

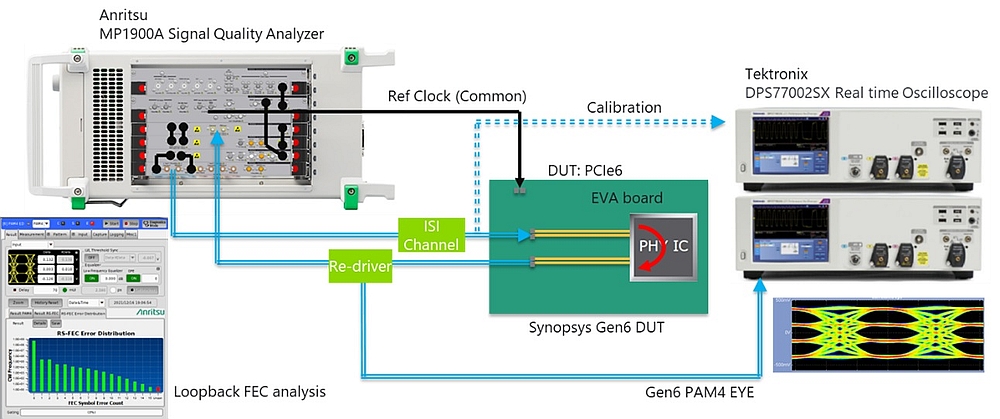

PCIe 6.0 utilise la correction d’erreur directe (FEC) comme technologie clé pour assurer l’intégrité des signaux 32-Gbaud PAM4 (64 Gbps), à faible SRN, affectés par la perte du chemin de transmission. Il en résulte une plus grande complexité associée à l’évaluation des dispositifs sous test (DUT). La démonstration a mis en œuvre une solution de test utilisant la calibration automatique de la spécification de base et l’évaluation de la qualité du signal par un oscilloscope temps réel DPO70000SX de Tektronix, combiné avec l’analyseur de signaux MP1900A d’Anritsu supportant l’analyse de correction d’erreur pour mesurer les erreurs de symboles FEC en temps réel.

Dans le cadre de cette démonstration, l’analyseur MP1900A génère un signal conforme aux contraintes, calibré par un oscilloscope DPO70000SX de Tektronix selon la spécification de base PCI Express 6.0. Le signal est transmis à l’IP PCI Express 6.0 de Synopsys pour mesurer les erreurs de bits à l’aide du compteur d’erreurs interne de l’objet sous test. De plus, les erreurs de bits sont mesurées par le détecteur d’erreurs MP1900A PAM4 en mode Loopback de l’objet sous test. Grâce à sa fonction FEC, le MP1900A analyse et affiche les erreurs corrigées/non corrigées FEC et le taux d’erreur post-FEC, tandis que l’oscilloscope en temps réel Tektronix DPO70000SX analyse les formes d’onde du signal de l’objet sous test.

Outre le test de base PCIe 6.0, un test complet PCIe 5.0 LEQ a été également présenté.

Le Signal Quality Analyzer-R MP1900A est un testeur de taux d’erreur (BERT) permettant d’évaluer la performance des interfaces à haut débit, telles que PCIe 6.0, PCIe 3.0 à 5.0, et USB3.2/4.0, ainsi que les interfaces de communication ultra large bande, notamment 400 GbE/800 GbE. C’est un instrument certifié PCI-SIG pour les tests de conformité jusqu’à PCIe 5.0.