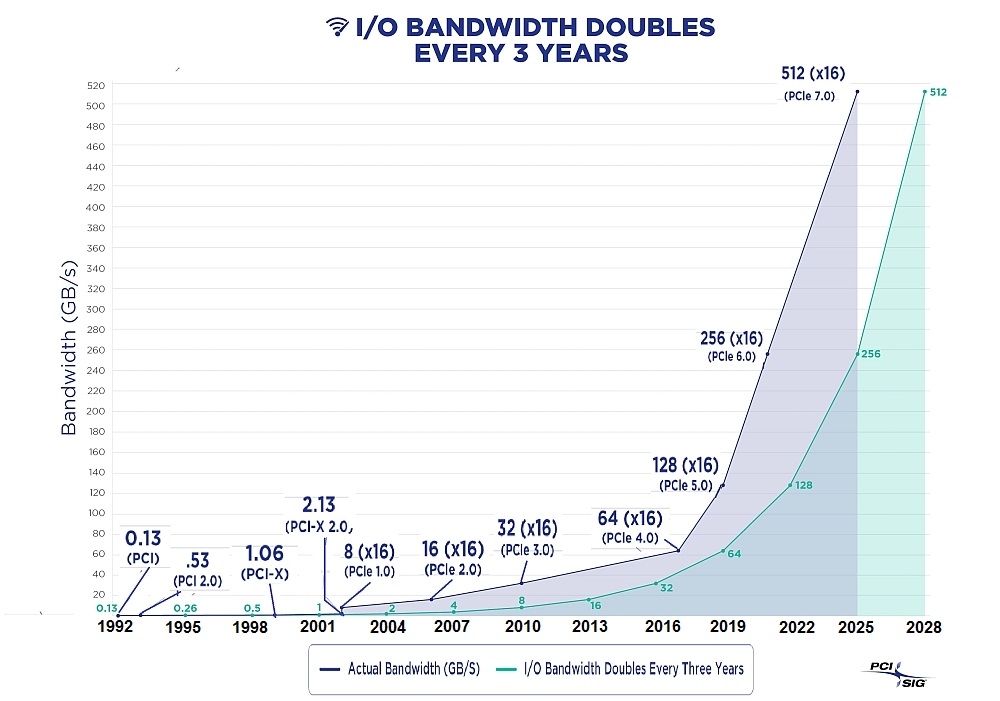

- En une trentaine d’années, le bus PCI a régulièrement évolué pour offrir davantage de performances en termes de transmission de données.

- En 2002, le PCI a connu une transformation majeure passant d’une architecture de bus parallèle à une architecture bus série baptisée PCI Express ou PCIe.

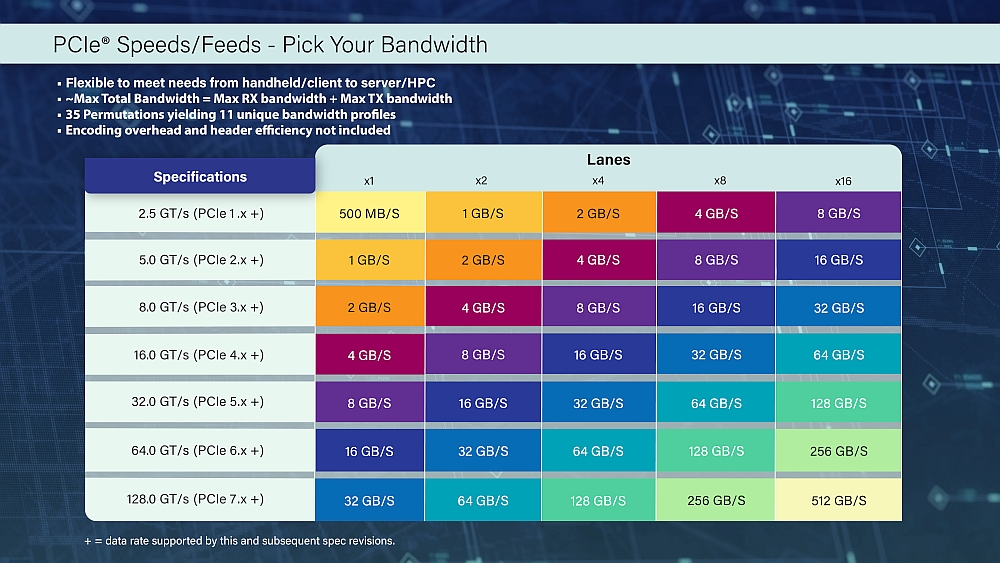

- L’actuelle version PCIe 6.0 permet d’atteindre une vitesse maximale théorique de transfert de données de 256 Go/s.

- La spécification PCI Express® (PCIe) 7.0 entend doubler la vitesse de données qui pourrait atteindre 512 Go/s en configuration de liaisons x16.

- Les spécifications du standard PCIe 7.0 devraient être publiées pour les membres du consortium PCI-SIG® en 2025.

Auteur : Youssef Belgnaoui – Actutem – « copyright – tous droits réservés »

Les groupes de travail techniques du PCI-SIG développent la spécification PCIe 7.0 avec pour objectif de :

– fournir un débit binaire brut de 128 GT/s et jusqu’à 512 Go/s de manière bidirectionnelle via une configuration x16.

– de mettre en œuvre la signalisation PAM4 (modulation d’amplitude d’impulsion à 4 niveaux)

– se concentrer sur les paramètres et la portée du canal

d’assurer des faible latence et une transmission de données de haute fiabilité

– améliorer l’efficacité énergétique

– maintenir la rétrocompatibilité avec toutes les générations PCIe précédentes.

Les premières versions de la technologie PCI mettaient en œuvre un bus parallèle qui permettait d’atteindre des vitesses de transmission de données de plusieurs centaines de mégaoctets par seconde. Ce qui correspondait aux besoins dans les années 1990 pour les applications de graphisme, de stockage et de mise en réseau.

En 2002, PCI-SIG a fait évoluer la structure du bus PCI en passant d’un concept de bus parallèle à un concept de bus série multi-liens qui a donné naissance au bus PCI Express ou PCIe. Cette évolution a permis de prendre en charge des vitesses de transfert de données de l’ordre du gigaoctet par seconde afin de s’adapter aux cadences attendues par des disques durs plus rapides et à l’Ethernet 100Mbit.

Alors que le PCI fonctionnait avec un seul bus de 32 bits opérant de manière bidirectionnel alterné, le PCI Express met en œuvre une interface série à base de lignes bidirectionnelles. Les ports PCIe ×1, ×2, ×4, ×8, ×16 se distinguent par le nombre de connecteurs de ligne dont ils disposent (respectivement 1, 2, 4, 8, 16 ou 32 lignes maximum). En pratique, le PCIe 6.0 autorise une vitesse de transfert de 256 Go/s en x16.

Le consortium PCI-SIG a fait évoluer progressivement les spécifications du bus PCI dont la cadence de transmission de données a doublé tous les trois ans afin de répondre aux attentes des applications informatiques et des marchés émergents.

La spécification PCIe 7.0 vise à répondre aux besoins des applications émergentes telles que l’Ethernet 800 G, les applications mettant en œuvre des techniques d’intelligence artificielle (IA) et de machine learning (ML), les plateformes Cloud, l’informatique quantique, les centres de données hyperscale, l’informatique à haute performance (HPC)…

- À propos de PCI-SIG

Le consortium PCI-SIG gère les spécifications PCI en tant que normes industrielles ouvertes. L’organisation définit des spécifications du bus PCI conformément aux besoins de ses 900 membres.